Page 35 - DCAP104_EXPOSURE_TO_COMPUTER_DISCPLINES

P. 35

Exposure to Computer Disciplines

Notes

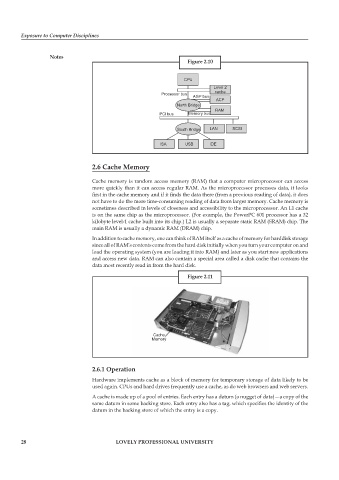

Figure 2.10

CPU

Level 2

cache

Processor bus

AGP bus

ACP

North Bridge

RAM

PCl bus Memory bus

South Bridge LAN SCSI

ISA USB IDE

2.6 Cache Memory

Cache memory is random access memory (RAM) that a computer microprocessor can access

more quickly than it can access regular RAM. As the microprocessor processes data, it looks

first in the cache memory and if it finds the data there (from a previous reading of data), it does

not have to do the more time-consuming reading of data from larger memory. Cache memory is

sometimes described in levels of closeness and accessibility to the microprocessor. An L1 cache

is on the same chip as the microprocessor. (For example, the PowerPC 601 processor has a 32

kilobyte level-1 cache built into its chip.) L2 is usually a separate static RAM (SRAM) chip. The

main RAM is usually a dynamic RAM (DRAM) chip.

In addition to cache memory, one can think of RAM itself as a cache of memory for harddisk storage

since all of RAM’s contents come from the hard disk initially when you turn your computer on and

load the operating system (you are loading it into RAM) and later as you start new applications

and access new data. RAM can also contain a special area called a disk cache that contains the

data most recently read in from the hard disk.

Figure 2.11

2.6.1 Operation

Hardware implements cache as a block of memory for temporary storage of data likely to be

used again. CPUs and hard drives frequently use a cache, as do web browsers and web servers.

A cache is made up of a pool of entries. Each entry has a datum (a nugget of data)—a copy of the

same datum in some backing store. Each entry also has a tag, which specifies the identity of the

datum in the backing store of which the entry is a copy.

28 LOVELY PROFESSIONAL UNIVERSITY