Page 107 - DCAP210_INTRODUCTION__TO_MICROPROCESSORS

P. 107

Unit 7: Memory Interfacing

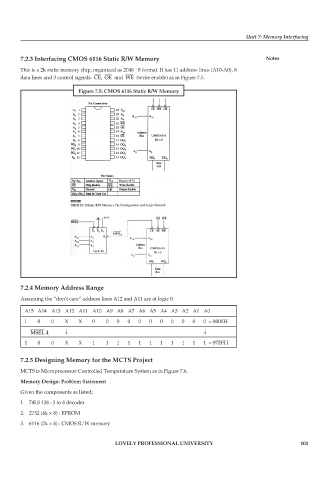

7.2.3 Interfacing CMOS 6116 Static R/W Memory Notes

This is a 2k static memory chip, organized as 2048 ´ 8 format. It has 11 address lines (A10-A0), 8

data lines and 3 control signals: CE, OE and WE (write enable) as in Figure 7.5.

Figure 7.5: CMOS 6116 Static R/W Memory

7.2.4 Memory Address Range

Assuming the “don’t care” address lines A12 and A11 are at logic 0.

A15 A14 A13 A12 A11 A10 A9 A8 A7 A6 A5 A4 A3 A2 A1 A0

1 0 0 X X 0 0 0 0 0 0 0 0 0 0 0 = 8000H

MSEL 4 ↓ ↓

1 0 0 X X 1 1 1 1 1 1 1 1 1 1 1 = 87FFH

7.2.5 Designing Memory for the MCTS Project

MCTS is Microprocessor-Controlled Temperature System as in Figure 7.6.

Memory Design: Problem Statement

Given the components as listed;

1. 74LS 138 : 3 to 8 decoder

2. 2732 (4k × 8) : EPROM

3. 6116 (2k × 8) : CMOS R/W memory

LOVELY PROFESSIONAL UNIVERSITY 101