Page 174 - DCAP103_Principle of operating system

P. 174

Unit 5: Memory Management

resulting in a trap to the operating system. If it is valid, then the value of the offset is added to Notes

the value of the base, resulting in a 32-bit linear address. This address is then translated into

a physical address. As pointed out previously, each segment is paged, and each page is 4 KB.

A page table may thus consist of up to 1 million entries. Because each entry consists of 4 bytes,

each process may need up to 4 MB of physical-address space for the page table alone. Clearly,

we would not want to allocate the page table contiguously in main memory. The solution

adopted in the 386 is to use a two-level paging scheme. The linear address is divided into a

page number consisting of 20 bits, and a page offset consisting of 12 bits. Since we page the

page table, the page number is further divided into a 10-bit page directory pointer and a 10-bit

page table pointer. The logical address is as follows:

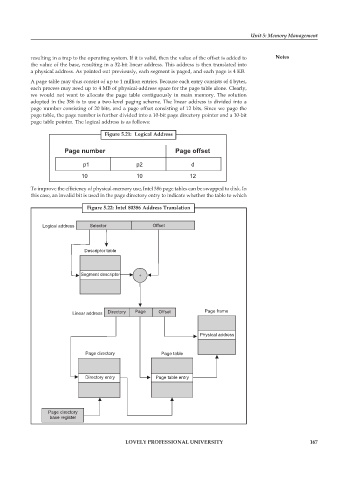

Figure 5.21: Logical Address

Page number Page offset

p1 p2 d

10 10 12

To improve the efficiency of physical-memory use, Intel 386 page tables can be swapped to disk. In

this case, an invalid bit is used in the page directory entry to indicate whether the table to which

Figure 5.22: Intel 80386 Address Translation

Logical address Selector Offset

Descriptor table

Segment descriptor +

Linear address Directory Page Offset Page frame

Physical address

Page directory Page table

Directory entry Page table entry

Page directory

base register

LOVELY PROFESSIONAL UNIVERSITY 167