Page 241 - DCAP108_DIGITAL_CIRCUITS_AND_LOGIC_DESIGNS

P. 241

Digital Circuits and Logic Design

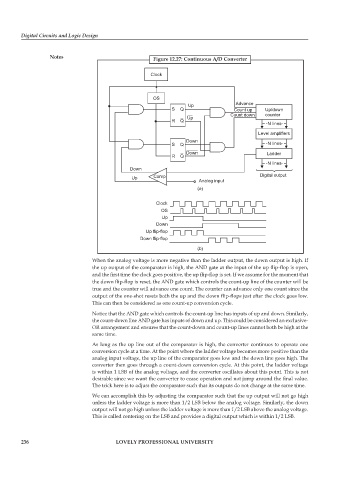

Notes Figure 12.27: Continuous A/D Converter

Clock

OS

Advance

Up

S Q Count up Up/down

Count down counter

Up

R Q

N lines

Level amplifiers

Down

S Q N lines

Down Ladder

R Q

N lines

Down

Up Comp Digital output

Analog input

a

()

Clock

OS

Up

Down

Up flip-flop

Down flip-flop

b

()

When the analog voltage is more negative than the ladder output, the down output is high. If

the up output of the comparator is high, the AND gate at the input of the up flip-flop is open,

and the first time the clock goes positive, the up flip-flop is set. If we assume for the moment that

the down flip-flop is reset, the AND gate which controls the count-up line of the counter will be

true and the counter will advance one count. The counter can advance only one count since the

output of the one-shot resets both the up and the down flip-flops just after the clock goes low.

This can then be considered as one count-up conversion cycle.

Notice that the AND gate which controls the count-up line has inputs of up and down. Similarly,

the count-down line AND gate has inputs of down and up. This could be considered an exclusive-

OR arrangement and ensures that the count-down and count-up lines cannot both be high at the

same time.

As long as the up line out of the comparator is high, the converter continues to operate one

conversion cycle at a time. At the point where the ladder voltage becomes more positive than the

analog input voltage, the up line of the comparator goes low and the down line goes high. The

converter then goes through a count-down conversion cycle. At this point, the ladder voltage

is within 1 LSB of the analog voltage, and the converter oscillates about this point. This is not

desirable since we want the converter to cease operation and not jump around the final value.

The trick here is to adjust the comparator such that its outputs do not change at the same time.

We can accomplish this by adjusting the comparator such that the up output will not go high

unless the ladder voltage is more than 1/2 LSB below the analog voltage. Similarly, the down

output will not go high unless the ladder voltage is more than 1/2 LSB above the analog voltage.

This is called centering on the LSB and provides a digital output which is within 1/2 LSB.

236 LOVELY PROFESSIONAL UNIVERSITY