Page 182 - DCAP108_DIGITAL_CIRCUITS_AND_LOGIC_DESIGNS

P. 182

Unit 10: Clocked Sequential Circuits

The corresponding state diagram is shown below: Notes

Apply the state assignment guidelines to the state diagram shown below:

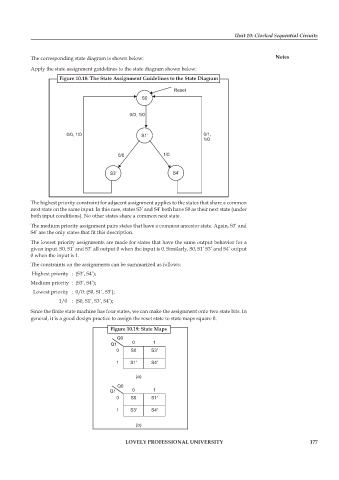

Figure 10.18: The State Assignment Guidelines to the State Diagram

The highest priority constraint for adjacent assignment applies to the states that share a common

next state on the same input. In this case, states S3’ and S4’ both have S0 as their next state (under

both input conditions). No other states share a common next state.

The medium priority assignment pairs states that have a common ancestor state. Again, S3’ and

S4’ are the only states that fit this description.

The lowest priority assignments are made for states that have the same output behavior for a

given input. S0, S1’ and S3’ all output 0 when the input is 0. Similarly, S0, S1’ S3’ and S4’ output

0 when the input is 1.

The constraints on the assignments can be summarized as follows:

Highest priority : (S3’, S4’);

Medium priority : (S3’, S4’);

Lowest priority : 0/0: (S0, S1’, S3’);

1/0 : (S0, S1’, S3’, S4’);

Since the finite state machine has four states, we can make the assignment onto two state bits. In

general, it is a good design practice to assign the reset state to state maps square 0.

Figure 10.19: State Maps

Q0

Q1 0 1

0 S0 S3′

1 S1′ S4′

(a)

Q0

Q1 0 1

0 S0 S1′

1 S3′ S4′

(b)

LOVELY PROFESSIONAL UNIVERSITY 177