Page 90 - DCAP108_DIGITAL_CIRCUITS_AND_LOGIC_DESIGNS

P. 90

Unit 5: Combinational Circuits

Notes

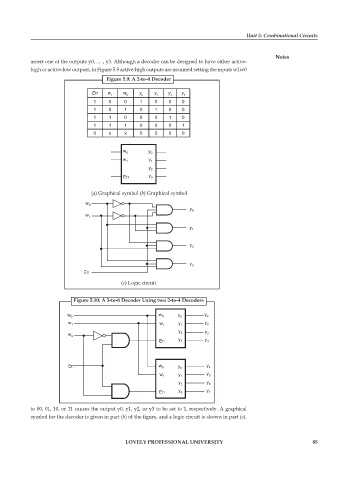

assert one of the outputs y0, .... , y3. Although a decoder can be designed to have either active-

high or active-low outputs, in Figure 5.9 active-high outputs are assumed setting the inputs w1w0

Figure 5.9: A 2-to-4 Decoder

En w 1 w 0 y 0 y 1 y 2 y 3

1 0 0 1 0 0 0

1 0 1 0 1 0 0

1 1 0 0 0 1 0

1 1 1 0 0 0 1

0 x x 0 0 0 0

(a) Graphical symbol (b) Graphical symbol

(c) Logic circuit

Figure 5.10: A 3-to-8 Decoder Using two 2-to-4 Decoders

w 0 w 0 y 0 y 0

w 1 w 1 y 1 y 2

y y

w 2 2 2

En y 3 y 3

En w 0 y 0 y 4

w y y 5

1 1

y y

2 6

En y 3 y 7

to 00, 01, 10, or 11 causes the output y0, y1, y2, or y3 to be set to 1, respectively. A graphical

symbol for the decoder is given in part (b) of the figure, and a logic circuit is shown in part (c).

LOVELY PROFESSIONAL UNIVERSITY 85