Page 86 - DCAP108_DIGITAL_CIRCUITS_AND_LOGIC_DESIGNS

P. 86

Unit 5: Combinational Circuits

Notes

Truth table

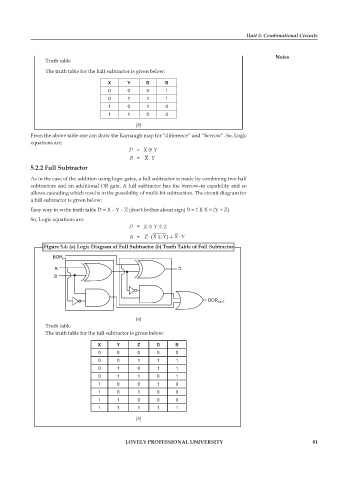

The truth table for the half subtractor is given below:

X Y D B

0 0 0 1

0 1 1 1

1 0 1 0

1 1 0 0

(b)

From the above table one can draw the Karnaugh map for “difference” and “borrow”. So, Logic

equations are:

D = X ⊕ Y

B = XY∙

5.2.2 Full Subtractor

As in the case of the addition using logic gates, a full subtractor is made by combining two half

subtractors and an additional OR gate. A full subtractor has the borrow–in capability and so

allows cascading which results in the possibility of multi-bit subtraction. The circuit diagram for

a full subtractor is given below:

Easy way to write truth table D = X – Y – Z (don’t bother about sign) B = 1 If X < (Y + Z)

So, Logic equations are:

D = X ⊕ Y ⊕ Z

·

B = ZX·( ⊕ Y) + X Y

Figure 5.4: (a) Logic Diagram of Full Subtractor (b) Truth Table of Full Subtractor

(a)

Truth table

The truth table for the full subtractor is given below:

X Y Z D B

0 0 0 0 0

0 0 1 1 1

0 1 0 1 1

0 1 1 0 1

1 0 0 1 0

1 0 1 0 0

1 1 0 0 0

1 1 1 1 1

(b)

LOVELY PROFESSIONAL UNIVERSITY 81