Page 160 - DCAP210_INTRODUCTION__TO_MICROPROCESSORS

P. 160

Introduction to Microprocessors

Notes

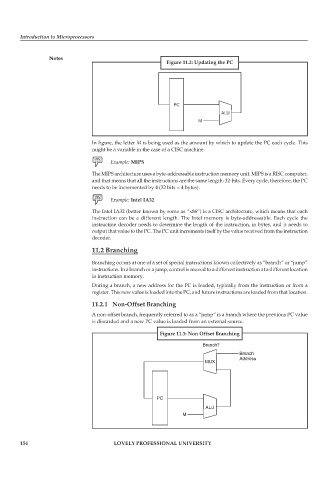

Figure 11.2: Updating the PC

In figure, the letter M is being used as the amount by which to update the PC each cycle. This

might be a variable in the case of a CISC machine.

Example: MIPS

The MIPS architecture uses a byte-addressable instruction memory unit. MIPS is a RISC computer,

and that means that all the instructions are the same length: 32-bits. Every cycle, therefore, the PC

needs to be incremented by 4 (32 bits = 4 bytes).

Example: Intel IA32

The Intel IA32 (better known by some as “x86”) is a CISC architecture, which means that each

instruction can be a different length. The Intel memory is byte-addressable. Each cycle the

instruction decoder needs to determine the length of the instruction, in bytes, and it needs to

output that value to the PC. The PC unit increments itself by the value received from the instruction

decoder.

11.2 Branching

Branching occurs at one of a set of special instructions known collectively as “branch” or “jump”

instructions. In a branch or a jump, control is moved to a different instruction at a different location

in instruction memory.

During a branch, a new address for the PC is loaded, typically from the instruction or from a

register. This new value is loaded into the PC, and future instructions are loaded from that location.

11.2.1 Non-Offset Branching

A non-offset branch, frequently referred to as a “jump” is a branch where the previous PC value

is discarded and a new PC value is loaded from an external source.

Figure 11.3: Non Offset Branching

154 LOVELY PROFESSIONAL UNIVERSITY