Page 106 - DCAP108_DIGITAL_CIRCUITS_AND_LOGIC_DESIGNS

P. 106

Unit 6: Implementation of Combinational Logic Circuit

example, where n = 4. Let A = a a a a and B = b b b b . Define a set of intermediate signals called Notes

3 2 1 0 3 2 1 0

i , i , i , and i . Each signal, i , is 1 if the bits of A and B with the same index are equal.

3 2 1 0 k

That is, i = a Å b . The comparator’s AeqB output is then given by

k k k

AeqB = i i i i

3 2 1 0

An expression for the AgtB output can be derived by considering the bits of A and B in the order

from the most-significant bit to the least-significant bit. The first bit-position, k, at which a and

k

b differ determines whether A is less than or greater than B. If a = 0 and bk = 1, then A < B. But

k

k

if ak = 1 and bk = 0, then A > B. The AgtB output is defined by

AgtB = ab +i ab +i ia b+ ii ia b

3 21 00

3 21 1

32 2

33

The ik signals ensure that only the first digits, considered from the left to the right, of A and B

that differ determine the value of AgtB.

The AltB output can be derived by using the other two outputs as

AltB = AeqB + AgtB

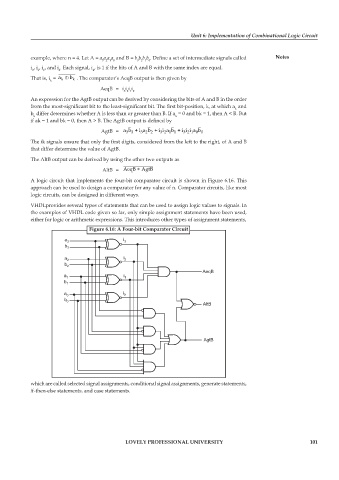

A logic circuit that implements the four-bit comparator circuit is shown in Figure 6.16. This

approach can be used to design a comparator for any value of n. Comparator circuits, like most

logic circuits, can be designed in different ways.

VHDLprovides several types of statements that can be used to assign logic values to signals. In

the examples of VHDL code given so far, only simple assignment statements have been used,

either for logic or arithmetic expressions. This introduces other types of assignment statements,

Figure 6.16: A Four-bit Comparator Circuit

which are called selected signal assignments, conditional signal assignments, generate statements,

if-then-else statements, and case statements.

LOVELY PROFESSIONAL UNIVERSITY 101