Page 117 - DCAP108_DIGITAL_CIRCUITS_AND_LOGIC_DESIGNS

P. 117

Digital Circuits and Logic Design

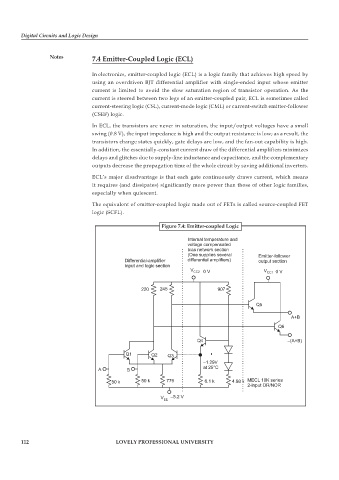

Notes 7.4 Emitter-Coupled Logic (ECL)

In electronics, emitter-coupled logic (ECL) is a logic family that achieves high speed by

using an overdriven BJT differential amplifier with single-ended input whose emitter

current is limited to avoid the slow saturation region of transistor operation. As the

current is steered between two legs of an emitter-coupled pair, ECL is sometimes called

current-steering logic (CSL), current-mode logic (CML) or current-switch emitter-follower

(CSEF) logic.

In ECL, the transistors are never in saturation, the input/output voltages have a small

swing (0.8 V), the input impedance is high and the output resistance is low; as a result, the

transistors change states quickly, gate delays are low, and the fan-out capability is high.

In addition, the essentially-constant current draw of the differential amplifiers minimizes

delays and glitches due to supply-line inductance and capacitance, and the complementary

outputs decrease the propagation time of the whole circuit by saving additional inverters.

ECL’s major disadvantage is that each gate continuously draws current, which means

it requires (and dissipates) significantly more power than those of other logic families,

especially when quiescent.

The equivalent of emitter-coupled logic made out of FETs is called source-coupled FET

logic (SCFL).

Figure 7.4: Emitter-coupled Logic

112 LOVELY PROFESSIONAL UNIVERSITY