Page 207 - DCAP108_DIGITAL_CIRCUITS_AND_LOGIC_DESIGNS

P. 207

Digital Circuits and Logic Design

Notes On the fourth clock pulse, the inverse of the last flip-flop, now a 0 will be shifted to the first

flip-flop, giving the state 011. On the fifth and sixth clock pulse, using the same reasoning, we will

get the states 001 and 000, which is the initial state again. Hence, this Johnson counter has six

distinct states: 000, 100, 110, 111, 011 and 001, and the sequence is repeated so long as there is

input pulse. Thus, this is a MOD-6 Johnson counter.

The MOD number of a Johnson counter is twice the number of flip-flops. In the example above,

three flip-flops were used to create the MOD-6 Johnson counter. So, for a given MOD number, a

Johnson counter requires only half the number of flip-flops needed for a ring counter. However,

a Johnson counter requires decoding gates whereas a ring counter does not. As with the binary

counter, one logic gate (AND gate) is required to decode each state, but with the Johnson counter,

each gate requires only two inputs, regardless of the number of flip-flops in the counter. Note that

we are comparing with the binary counter using the speed up technique discussed above. The

reason for this is that for each state, two of the N flip-flops used will be in a unique combination

of states. In the example above, the combination Q = Q = 0 occurs only once in the counting

2

1

sequence, at the count of 0. The state 010 does not occur. Thus, an AND gate with inputs (not

Q ) and (not Q ) can be used to decode for this state. The same characteristic is shared by all the

2

2

other states in the sequence.

A Johnson counters represent a middle ground between ring counters and binary counters. A

Johnson counter requires fewer flip-flops than a ring counter but generally more than a binary

counter; it has more decoding circuitry than a ring counter but less than a binary counter. Thus,

it sometimes represents a logical choice for certain applications.

Alan Jones first appeared in summer 1984 in the RRCA publication footnotes

using the calibrated bicycle method announced the Jones Counter.

11.3.8 Loadable/Presettable Counters

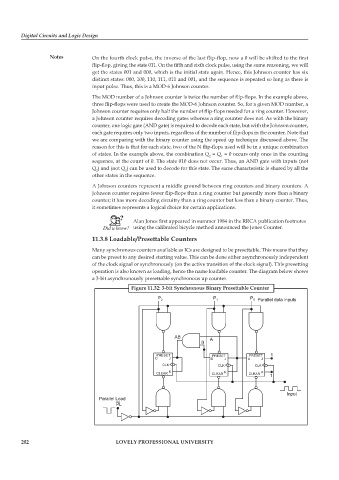

Many synchronous counters available as ICs are designed to be presettable. This means that they

can be preset to any desired starting value. This can be done either asynchronously independent

of the clock signal or synchronously (on the active transition of the clock signal). This presetting

operation is also known as loading, hence the name loadable counter. The diagram below shows

a 3-bit asynchronously presettable synchronous up counter.

Figure 11.32: 3-bit Synchronous Binary Presettable Counter

202 LOVELY PROFESSIONAL UNIVERSITY