Page 205 - DCAP108_DIGITAL_CIRCUITS_AND_LOGIC_DESIGNS

P. 205

Digital Circuits and Logic Design

Notes From the diagram, we can see that COUNT-UP and COUNT-DOWN are used as control inputs

to determine whether the normal flip-flop outputs or the inverted ones are fed into the J-K inputs

of the following flip-flops. If neither is at logic level 1, the counter does not count and if both are

at logic level 1, all the bits of the counter toggle at every clock pulse. The OR gate allows either

of the two outputs which have been enabled to be fed into the next flip-flop. As with the binary

up and binary down counter, the speed up techniques apply.

11.3.4 MOD-N/Divide-by-N Counters

Normal binary counter counts from 0 to 2 – 1, where N is the number of bits/flip-flops in the

N

counter. In some cases, we want it to count to numbers other than 2 – 1. This can be done by

N

allowing the counter to skip states that are normally part of the counting sequence. There are a

few methods of doing this. One of the most common methods is to use the CLEAR input on the

flip-flops.

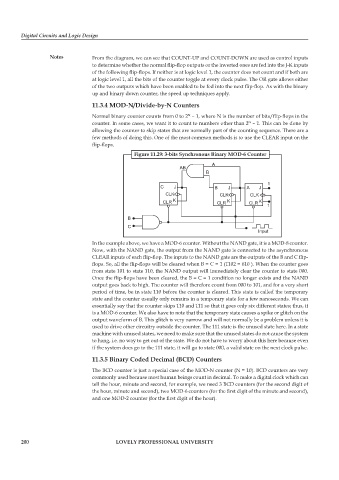

Figure 11.29: 3-bits Synchronous Binary MOD-6 Counter

A

AB

B

1

C J B J A J

CLK CLK CLK

CLR K CLR K CLR K

1

B

C

Input

In the example above, we have a MOD-6 counter. Without the NAND gate, it is a MOD-8 counter.

Now, with the NAND gate, the output from the NAND gate is connected to the asynchronous

CLEAR inputs of each flip-flop. The inputs to the NAND gate are the outputs of the B and C flip-

flops. So, all the flip-flops will be cleared when B = C = 1 (1102 = 610 ). When the counter goes

from state 101 to state 110, the NAND output will immediately clear the counter to state 000.

Once the flip-flops have been cleared, the B = C = 1 condition no longer exists and the NAND

output goes back to high. The counter will therefore count from 000 to 101, and for a very short

period of time, be in state 110 before the counter is cleared. This state is called the temporary

state and the counter usually only remains in a temporary state for a few nanoseconds. We can

essentially say that the counter skips 110 and 111 so that it goes only six different states; thus, it

is a MOD-6 counter. We also have to note that the temporary state causes a spike or glitch on the

output waveform of B. This glitch is very narrow and will not normally be a problem unless it is

used to drive other circuitry outside the counter. The 111 state is the unused state here. In a state

machine with unused states, we need to make sure that the unused states do not cause the system

to hang, i.e. no way to get out of the state. We do not have to worry about this here because even

if the system does go to the 111 state, it will go to state 000, a valid state on the next clock pulse.

11.3.5 Binary Coded Decimal (BCD) Counters

The BCD counter is just a special case of the MOD-N counter (N = 10). BCD counters are very

commonly used because most human beings count in decimal. To make a digital clock which can

tell the hour, minute and second, for example, we need 3 BCD counters (for the second digit of

the hour, minute and second), two MOD-6 counters (for the first digit of the minute and second),

and one MOD-2 counter (for the first digit of the hour).

200 LOVELY PROFESSIONAL UNIVERSITY