Page 201 - DCAP108_DIGITAL_CIRCUITS_AND_LOGIC_DESIGNS

P. 201

Digital Circuits and Logic Design

Notes

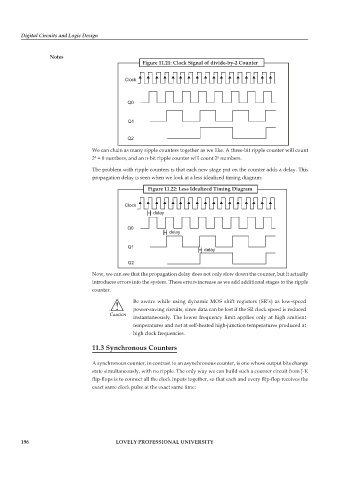

Figure 11.21: Clock Signal of divide-by-2 Counter

We can chain as many ripple counters together as we like. A three-bit ripple counter will count

2 = 8 numbers, and an n-bit ripple counter will count 2 numbers.

3

n

The problem with ripple counters is that each new stage put on the counter adds a delay. This

propagation delay is seen when we look at a less idealized timing diagram:

Figure 11.22: Less Idealized Timing Diagram

Clock

H delay

Q0

H delay

Q1

H delay

Q2

Now, we can see that the propagation delay does not only slow down the counter, but it actually

introduces errors into the system. These errors increase as we add additional stages to the ripple

counter.

Be aware while using dynamic MOS shift registers (SR’s) as low-speed

power-saving circuits, since data can be lost if the SR clock speed is reduced

instantaneously. The lower frequency limit applies only at high ambient

temperatures and not at self-heated high-junction temperatures produced at

high clock frequencies.

11.3 Synchronous Counters

A synchronous counter, in contrast to an asynchronous counter, is one whose output bits change

state simultaneously, with no ripple. The only way we can build such a counter circuit from J-K

flip-flops is to connect all the clock inputs together, so that each and every flip-flop receives the

exact same clock pulse at the exact same time:

196 LOVELY PROFESSIONAL UNIVERSITY