Page 202 - DCAP108_DIGITAL_CIRCUITS_AND_LOGIC_DESIGNS

P. 202

Unit 11: Registers and Counters

Notes

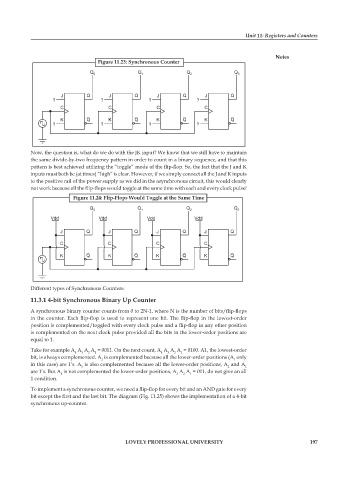

Figure 11.23: Synchronous Counter

Now, the question is, what do we do with the JK input? We know that we still have to maintain

the same divide-by-two frequency pattern in order to count in a binary sequence, and that this

pattern is best achieved utilizing the “toggle” mode of the flip-flop. So, the fact that the J and K

inputs must both be (at times) “high” is clear. However, if we simply connect all the J and K inputs

to the positive rail of the power supply as we did in the asynchronous circuit, this would clearly

not work because all the flip-flops would toggle at the same time with each and every clock pulse!

Figure 11.24: Flip-Flops Would Toggle at the Same Time

Different types of Synchronous Counters:

11.3.1 4-bit Synchronous Binary Up Counter

A synchronous binary counter counts from 0 to 2N-1, where N is the number of bits/flip-flops

in the counter. Each flip-flop is used to represent one bit. The flip-flop in the lowest-order

position is complemented/toggled with every clock pulse and a flip-flop in any other position

is complemented on the next clock pulse provided all the bits in the lower-order positions are

equal to 1.

Take for example A A A A = 0011. On the next count, A A A A = 0100. A1, the lowest-order

3

4

3

4

2

1

2

1

bit, is always complemented. A is complemented because all the lower-order positions (A only

2

1

in this case) are 1’s. A is also complemented because all the lower-order positions, A and A

2

1

3

are 1’s. But A is not complemented the lower-order positions, A A A = 011, do not give an all

2

1

3

4

1 condition.

To implement a synchronous counter, we need a flip-flop for every bit and an AND gate for every

bit except the first and the last bit. The diagram (Fig. 11.25) shows the implementation of a 4-bit

synchronous up-counter.

LOVELY PROFESSIONAL UNIVERSITY 197