Page 97 - DCAP108_DIGITAL_CIRCUITS_AND_LOGIC_DESIGNS

P. 97

Digital Circuits and Logic Design

Notes

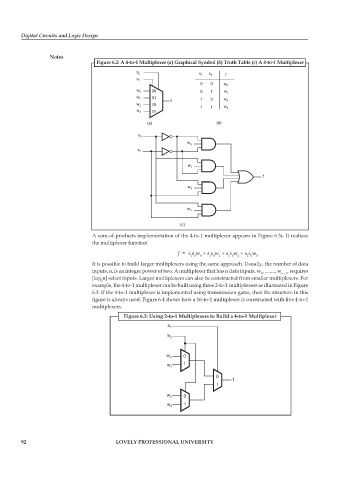

Figure 6.2: A 4-to-1 Multiplexer (a) Graphical Symbol (b) Truth Table (c) A 4-to-1 Multiplexer

s 0

f

s 1 s 0

s 1

0 0 w 0

00

w 0 0 1 w 1

01

w 1 1 0

f w 2

10

w 2

1 1 w 3

w 3 11

b

() ()

a

s 0

w 0

s 1

w 1

f

w 2

w 3

()

c

A sum-of-products implementation of the 4-to-1 multiplexer appears in Figure 6.3c. It realizes

the multiplexer function

f = ś ś w + ś s w + s ś w + s s w

1 0 0 1 0 1 1 0 2 1 0 3

It is possible to build larger multiplexers using the same approach. Usually, the number of data

inputs, n, is an integer power of two. A multiplexer that has n data inputs, w , ........, w n – 1 , requires

0

[log n] select inputs. Larger multiplexers can also be constructed from smaller multiplexers. For

2

example, the 4-to-1 multiplexer can be built using three 2-to-1 multiplexers as illustrated in Figure

6.3. If the 4-to-1 multiplexer is implemented using transmission gates, then the structure in this

figure is always used. Figure 6.4 shows how a 16-to-1 multiplexer is constructed with five 4-to-1

multiplexers.

Figure 6.3: Using 2-to-1 Multiplexers to Build a 4-to-1 Multiplexer

92 LOVELY PROFESSIONAL UNIVERSITY