Page 100 - DCAP108_DIGITAL_CIRCUITS_AND_LOGIC_DESIGNS

P. 100

Unit 6: Implementation of Combinational Logic Circuit

Notes

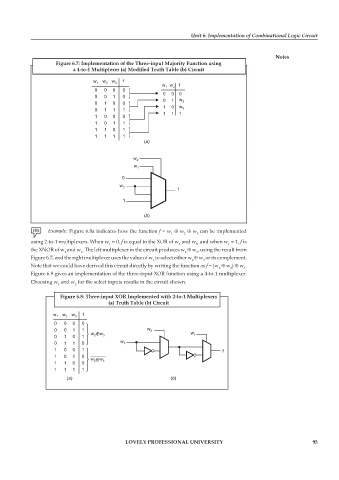

Figure 6.7: Implementation of the Three-input Majority Function using

a 4-to-1 Multiplexer (a) Modified Truth Table (b) Circuit

w 1 w 2 w 3 f

w 1 w 2 f

0 0 0 0

0 0 0

0 0 1 0

0 1 w 3

0 1 0 0

1 0 w

0 1 1 1 3

1 1 1

1 0 0 0

1 0 1 1

1 1 0 1

1 1 1 1

()

a

w 2

w 1

0

w 3

f

1

b

()

Figure 6.8a indicates how the function f = w ⊕ w ⊕ w can be implemented

1 2 3

using 2-to-1 multiplexers. When w = 0, f is equal to the XOR of w and w , and when w = 1, f is

2

1

3

1

the XNOR of w and w . The left multiplexer in the circuit produces w ⊕ w , using the result from

3

2

2

3

Figure 6.7, and the right multiplexer uses the value of w to select either w ⊕ w or its complement.

1

2

3

Note that we could have derived this circuit directly by writing the function as f = (w ⊕ w ) ⊕ w .

3

2

1

Figure 6.9 gives an implementation of the three-input XOR function using a 4-to-1 multiplexer.

Choosing w and w for the select inputs results in the circuit shown.

1 2

Figure 6.8: Three-input XOR Implemented with 2-to-1 Multiplexers

(a) Truth Table (b) Circuit

w 1 w 2 w 3 f

0 0 0 0

0 0 1 1 w 2

w w w 1

0 1 0 1 2 3

w

0 1 1 0 3

1 0 0 1 f

1 0 1 0

w 2 w 3

1 1 0 0

1 1 1 1

a

b

() ()

LOVELY PROFESSIONAL UNIVERSITY 95