Page 95 - DCAP210_INTRODUCTION__TO_MICROPROCESSORS

P. 95

Unit 6: The 8085 Microprocessor Architecture

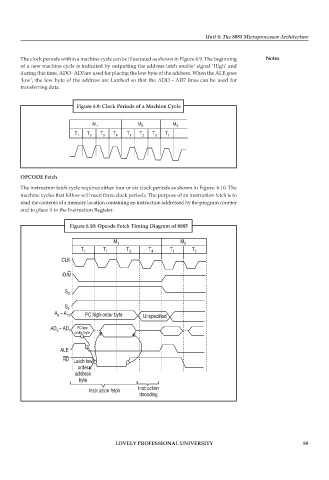

The clock periods within a machine cycle can be illustrated as shown in Figure 6.9. The beginning Notes

of a new machine cycle is indicated by outputting the address latch enable’ signal ‘High’ and

during this time, ADO- AD7are used for placing the low byte of the address. When the ALE goes

‘low’, the low byte of the address are Latched so that the ADO - AD7 lines can be used for

transferring data.

Figure 6.9: Clock Periods of a Machine Cycle

OPCODE Fetch

The instruction fetch cycle requires either four or six clock periods as shown in Figure. 6.10. The

machine cycles that follow will need three clock periods. The purpose of an instruction fetch is to

read the contents of a memory location containing an instruction addressed by the program counter

and to place it in the Instruction Register.

Figure 6.10: Opcode Fetch Timing Diagram of 8085

LOVELY PROFESSIONAL UNIVERSITY 89