Page 99 - DCAP210_INTRODUCTION__TO_MICROPROCESSORS

P. 99

Unit 6: The 8085 Microprocessor Architecture

Notes

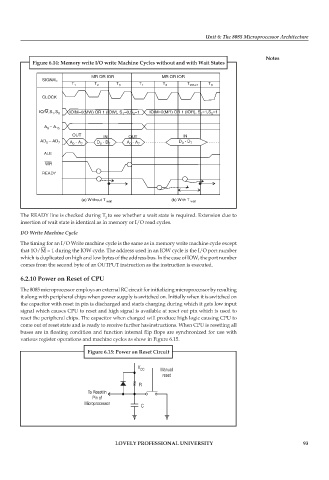

Figure 6.14: Memory write I/O write Machine Cycles without and with Wait States

The READY line is checked during T to see whether a wait state is required. Extension due to

2

insertion of wait state is identical as in memory or I/O read cycles.

I/O Write Machine Cycle

The timing for an I/O Write machine cycle is the same as in memory write machine cycle except

that 1O/M = 1 during the IOW cycle. The address used in an IOW cycle is the I/O port number

which is duplicated on high and low bytes of the address bus. In the case of IOW, the port number

comes from the second byte of an OUTPUT instruction as the instruction is executed.

6.2.10 Power on Reset of CPU

The 8085 microprocessor employs an external RC circuit for initializing microprocessor by resulting

it along with peripheral chips when power supply is switched on. Initially when it is switched on

the capacitor with reset in pin is discharged and starts charging during which it gets low input

signal which causes CPU to reset and high signal is available at reset out pin which is used to

reset the peripheral chips. The capacitor when charged will produce high logic causing CPU to

come out of reset state and is ready to receive further hasinstructions. When CPU is resetting all

buses are in floating condition and function internal flip flops are synchronized for use with

various register operations and machine cycles as show in Figure 6.15.

Figure 6.15: Power on Reset Circuit

LOVELY PROFESSIONAL UNIVERSITY 93