Page 155 - DCAP108_DIGITAL_CIRCUITS_AND_LOGIC_DESIGNS

P. 155

Digital Circuits and Logic Design

Notes The NAND basic flip-flop circuit in Figure 9.2 (a) operates with inputs normally at 1 unless the

state of the flip-flop has to be changed. A 0 applied momentarily to the set input causes Q to go

to 1 and Q′ to go to 0, putting the flip-flop in the set state. When both inputs go to 0, both outputs

go to 1. This condition should be avoided in normal operation.

The first electronic flip-flop was invented in 1918 by William Henry Eccles

and F. W. Jordan.

9.2 Types of Flip-Flop

The types of flip-flop circuit that are being used in digital circuits. They can be classified according

to the number of inputs they possess and the manner in which they affect the binary state of the

flip-flop.

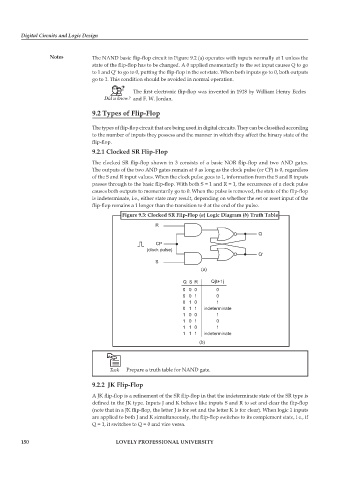

9.2.1 Clocked SR Flip-Flop

The clocked SR flip-flop shown in 3 consists of a basic NOR flip-flop and two AND gates.

The outputs of the two AND gates remain at 0 as long as the clock pulse (or CP) is 0, regardless

of the S and R input values. When the clock pulse goes to 1, information from the S and R inputs

passes through to the basic flip-flop. With both S = 1 and R = 1, the occurrence of a clock pulse

causes both outputs to momentarily go to 0. When the pulse is removed, the state of the flip-flop

is indeterminate, i.e., either state may result, depending on whether the set or reset input of the

flip-flop remains a 1 longer than the transition to 0 at the end of the pulse.

Figure 9.3: Clocked SR Flip-Flop (a) Logic Diagram (b) Truth Table

R

Q

CP

(clock pulse)

Q

S

()

a

Q SR Q(t+1)

0 0 0 0

0 0 1 0

0 1 0 1

0 1 1 indeterminate

1 0 0 1

1 0 1 0

1 1 0 1

1 1 1 indeterminate

b

()

Prepare a truth table for NAND gate.

9.2.2 JK Flip-Flop

A JK flip-flop is a refinement of the SR flip-flop in that the indeterminate state of the SR type is

defined in the JK type. Inputs J and K behave like inputs S and R to set and clear the flip-flop

(note that in a JK flip-flop, the letter J is for set and the letter K is for clear). When logic 1 inputs

are applied to both J and K simultaneously, the flip-flop switches to its complement state, i e., if

Q = 1, it switches to Q = 0 and vice versa.

150 LOVELY PROFESSIONAL UNIVERSITY