Page 252 - DCAP108_DIGITAL_CIRCUITS_AND_LOGIC_DESIGNS

P. 252

Unit 12: A/D and D/A Converters

count is less than or greater than the analog signal input, adjusting the bit values accordingly. The Notes

way the register counts is identical to the “trial-and-fit” method of decimal-to-binary conversion,

whereby different values of bits are tried from MSB to LSB to get a binary number that equals

the original decimal number. The advantage to this counting strategy is much faster results: the

DAC output converges on the analog signal input in much larger steps than with the 0-to-full

count sequence of a regular counter.

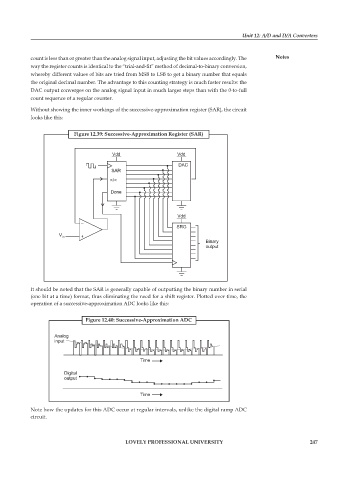

Without showing the inner workings of the successive-approximation register (SAR), the circuit

looks like this:

Figure 12.39: Successive-Approximation Register (SAR)

It should be noted that the SAR is generally capable of outputting the binary number in serial

(one bit at a time) format, thus eliminating the need for a shift register. Plotted over time, the

operation of a successive-approximation ADC looks like this:

Figure 12.40: Successive-Approximation ADC

Note how the updates for this ADC occur at regular intervals, unlike the digital ramp ADC

circuit.

LOVELY PROFESSIONAL UNIVERSITY 247